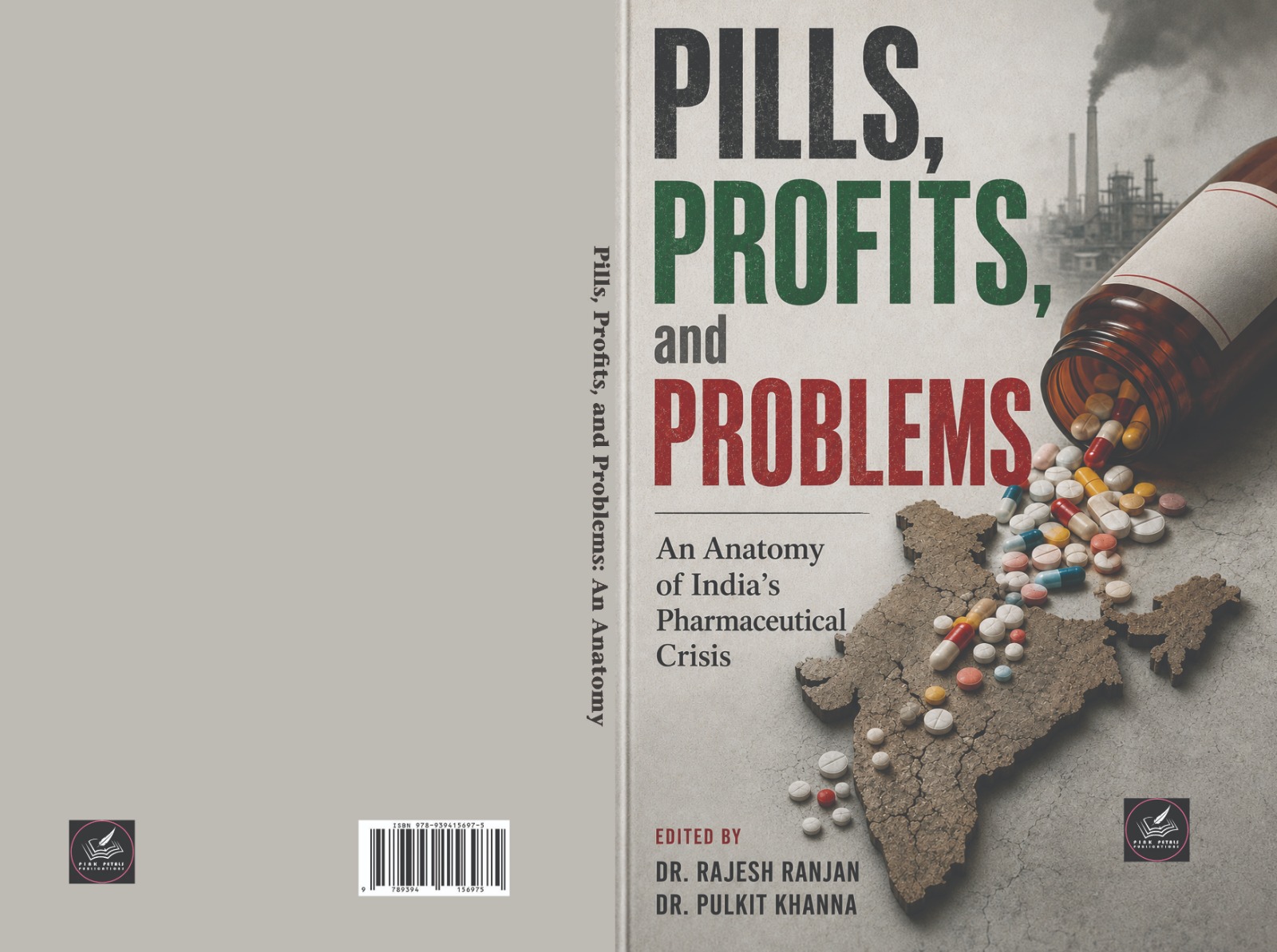

Recent PublicationPills, Profits, and Problems: An Anatomy of India’s Pharmaceutical Crisis

Published 13 May 2025

Description

Type: Open Access Book

Title: Pills, Profits, and Problems: An Anatomy of India’s Pharmaceutical Crisis

Edited by Dr. Rajesh Ranjan, Dr. Pulkit Khanna

ISBN: 978-93-94156-97-5

ISBN 93-94156-97-6

DOI:

Language: English

Published by Pink Petals Publication Pvt Ltd.

© 2025 This work is licensed under the Creative Commons Attribution 4.0 (CC-BY 4.0). It permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made. To view a copy of this license, visit https://creativecommons.org/licenses/by/4.0/

Table of Contents

Chapter

Pink Petals Publications offers authors extensive opportunities for open access publishing, ensuring their research meets funder requirements and reaches a wide audience. Authors can choose from various formats, including monographs, handbooks, textbooks, and shorter titles.

In addition to full-length books, authors can also publish individual chapters as open access, allowing for broader dissemination of their work. These chapters are accessible under Creative Commons licenses, enabling free access and download. Throughout the publishing process, Pink Petals Publications offers dedicated support, including assistance with funding, copyright, and publishing formats, ensuring a seamless experience for authors.

Pink Petals Publications is an Open Access publisher, committed to providing permanent and free online access to our books for readers without charging any publication fees for authors. Our approach offers numerous advantages:

Wide International Readership: Our books enjoy global accessibility, with an average monthly access of 400 times worldwide. Many of our publications exceed 10,000 readers within three years of release.

Impact and Accessibility: By ensuring perpetual online access, our publications remain impactful and meet Open Access requirements for research assessments.

Swift Publication: We strive to reach publishing decisions within twelve weeks of receiving a complete book proposal, supported by an agile and efficient production process.

Rigorous Peer-review and Editing: With a decade of experience collaborating with esteemed authors like Noam Chomsky, Amartya Sen, and Gordon Brown, Pink Petals Publications maintains exceptionally high standards in peer-review and editorial processes.

Innovation and Collaboration: We work closely with authors to explore innovative presentation methods for their research, such as embedding multimedia content or creating interactive editions.

High-quality Editions: Pink Petals Publications offers high-quality paperback, hardback, and digital editions at reasonable prices, ensuring global distribution and accessibility.

Copyright Ownership: Authors retain full copyright of their work, empowering them to control its usage and dissemination.

In summary, Pink Petals Publications' model emphasizes accessibility, impact, and author ownership while upholding rigorous academic standards and fostering collaboration and innovation.